# Query Processing On Heterogeneous Systems

vorgelegt von

Dipl.-Inf. Viktor Rosenfeld ORCID: 0000-0002-6001-4442

an der Fakultät IV – Elektrotechnik und Informatik der Technischen Universität Berlin zur Erlangung des akademischen Grades

Doktor der Ingenieurwissenschaften - Dr.-Ing. -

genehmigte Dissertation

#### Promotionsausschuss:

Vorsitzender: Prof. Dr. Matthias Böhm, Technische Universität Berlin Gutachter: Prof. Dr. Volker Markl, Technische Universität Berlin

Gutachter: Prof. Dr. Wolfgang Lehner, Technische Universität Dresden

Gutachter: Prof. Dr. Peter Boncz, Centrum Wiskunde & Informatica, Amsterdam,

und Vrije Universiteit Amsterdam

Tag der wissenschaftlichen Aussprache: 8. Dezember 2023

Berlin 2024

## Acknowledgments

I would not have been able to complete this PhD thesis without the help of many people, all of whom have my sincere gratitude.

First, I want to thank my advisor, Volker Markl, for providing me with the opportunity and resources to pursue my PhD. His leadership in creating a successful and highly regarded research group greatly enriched my experience. I also extend my thanks to Peter Boncz, Matthias Böhm, and Wolfgang Lehner for serving on my doctoral committee.

Before joining the DIMA group at TU Berlin, I was fortunate to work with Ulf Leser and Anke Lüdeling, who introduced me to academic research and inspired me to pursue a PhD.

I am grateful to my co-authors, Sebastian Breß, Max Heimel, Tilmann Rabl, Jonas Traub, Christoph Viebig, and Steffen Zeuch, or their invaluable contributions, and to my student Tobias Behrens for our fruitful collaboration. A special shout out goes to my long-time office mate Clemens Lutz. I benefited greatly from his deep technical knowledge and enjoyed our many engaging discussions, both on and off topic.

Teaching has always been an important part of my PhD journey, and I am grateful to Rudi Lemaitre and Haralampos Gavriilidis, for sharing my passion for it, not to mention the teaching load. Another special shout out goes to Gereon Dusella. His in-depth knowledge of academic regulations and passion for teaching made me a better teacher.

My sincere thanks go to Lutz Friedel, Claudia Gantzer, Melanie Neumann, and Anja Weymann for their technical and administrative support. I am also grateful to my colleagues Ankit Chaudhary, Dimitrios Giouroukis, Philipp Grulich, Aljoscha Lepping, Adrian Michalke, Dwi Nugroho, Ricardo Ramirez, Nils Schubert, and Ariane Ziehn for their help with project work, as well as to Martin Kiefer, Andreas Kunft, and Sebastian Schelter for their advice throughout my time at DIMA.

A highlight of my PhD journey was my internship at IBM Research Almaden, where I had the privilege of working with Rene Mueller, Fatma Özcan, and Pinar Tözün. Our collaboration was incredibly fruitful, and I am deeply grateful for their excellent mentorship and guidance.

Finally, I want to thank my family and friends for their support throughout the years.

### Abstract

Today's computing systems are highly heterogeneous, both in terms of the hardware that they are built from and the software that they run. This heterogeneity provides key benefits, since specialized processors provide the performance necessary to process increasing amounts of data, and specialized software system enable programmers with different needs and expertise to extract knowledge from data. However, the integration of heterogeneous hardware and software into a cohesive system poses many challenges, e.g., how to distribute work among heterogeneous processors, how to reduce the complexity of programming heterogeneous processors, and how to reduce overheads when moving data and computation between different software systems.

In this thesis, we investigate how heterogeneous hardware and software impacts query processing, and develop tools to manage this heterogeneity.

In our first contribution, we survey query processing systems that target both CPUs and GPUs. We develop a classification scheme to categorize how to distribute query processing tasks on these processors, and review techniques to program CPUs and GPUs in a query processing system, and to overcome the data transfer bottleneck. Our analysis shows that systems with dedicated GPUs require different strategies to distribute the workload than systems with integrated GPUs.

In our second contribution, we investigate how a query processing systems can automatically adapt its low-level operator implementation to the processor it runs on. First, we perform an extensive experimental analysis of different implementations of two data processing operators on various CPUs, GPUs, and an Intel Xeon Phi coprocessor. We find that every processor requires specific implementations to achieve high performance, that heuristics derived from the analysis of one processor are not necessarily transferable to others, and that some processors are more difficult to optimize for than others. Then, we develop two algorithms to find a fast operator implementation at runtime, which differ in the amount of information they incorporate during their search. Our evaluation of these algorithms shows that it is necessary to exploit information about processor characteristics to reduce the search time for a fast implementation.

In our third contribution, we focus on integrating query processing systems that run on the Java Virtual Machine (JVM) and those that execute native machine code. Concretely, we develop two approaches how to execute Java-based UDFs in a query processing engine written in C++. First, we transparently transform a tuple-based UDF into a UDF that processes an entire batch, which effectively eliminates the overhead of moving execution from the C++ engine into an embedded JVM. This approach works well if the UDF creates many objects, including Java strings. Second, we translate the UDF bytecode to LLVM IR and link it directly with the C++ engine. This approach works well if the UDF is compute-intensive.

Our investigation into a variety of heterogeneous hardware and software scenarios shows that we often face similar challenges when integrating them. Thus, the techniques investigated and developed in this thesis constitute effective building blocks to extract performance from today's heterogeneous computing systems.

## Zusammenfassung

Heutige Computersysteme sind außerordentlich heterogen. Sie bestehen aus vielseitig spezialisierter Hardware und führen unterschiedlichste Softwaresysteme aus. Einerseits bietet diese Heterogenität wesentliche Vorteile, da z.B. spezialisierte Prozessoren die notwendige Leistung für die Verarbeitung wachsender Datenmengen bereitstellen und spezialisierte Softwaresysteme Programmierern mit unterschiedlichen Anforderungen und Fachkenntnissen ermöglichen, Wissen aus Daten zu erschließen. Andererseits birgt die Integration heterogener Hard- und Software aber auch viele Herausforderungen. So stellt sich beispielweise die Frage, wie die Arbeitsteilung zwischen heterogenen Prozessoren erfolgen soll, wie sich die Komplexität der Programmierung heterogener Prozessoren reduzieren lässt und wie der Overhead bei der Übertragung von Daten und der Verteilung von Berechnungen zwischen verschiedenen Softwaresystemen minimiert werden kann.

In dieser Arbeit untersuchen wir, wie heterogene Hard- und Software die Anfrageverarbeitung beeinflusst, und entwickeln Werkzeuge, um diese Heterogenität zu bewältigen.

Im ersten Beitrag untersuchen wir Systeme, die die Anfrageverarbeitung auf CPUs und GPUs aufteilen. Hierfür entwickeln wir ein Klassifikationsschema, um Strategien zur Verteilung von Teilaufgaben der Anfrageverarbeitung auf diesen Prozessoren zu kategorisieren. Darüber hinaus untersuchen wir Methoden um die Architektur eines Anfragesystems an heterogene Prozessoren anzupassen und um langsame Datentransfers zwischen CPU und GPU zu vermeiden. Unsere Analyse zeigt, dass Systeme mit dedizierten GPUs andere Strategien zur Arbeitsaufteilung erfordern als Systeme mit integrierten GPUs.

Im zweiten Beitrag untersuchen wir, wie ein Anfrageverarbeitungssystem die Implementierung von datenverarbeitenden Operatoren automatisch an den Prozessor adaptieren kann, auf dem es ausgeführt wird. Hierfür führen wir zunächst eine umfangreiche experimentelle Analyse verschiedener Implementierungsvarianten für zwei Operatoren auf verschiedenen CPUs, GPUs und einem Intel Xeon Phi Coprozessor durch. Unsere Analyse zeigt, dass jeder Prozessor eine spezifische Implementierung benötigt, um Daten schnell zu verarbeiten. Darüber hinaus stellen wir fest, dass Heuristiken, die

aus der Analyse eines bestimmten Prozessors abgeleitet wurden, nicht unbedingt auf andere Prozessoren übertragbar sind und dass einige Prozessoren schwieriger zu optimieren sind als andere. Anschließend entwickeln wir zwei Algorithmen, die es einem Anfragesystem ermöglichen, automatisch eine schnelle Operatorimplementierung zu finden. Die Algorithmen unterscheiden sich in der Art der Informationen, die sie bei der Suche berücksichtigen. Unsere Auswertung dieser Algorithmen zeigt, dass es notwendig ist, Informationen über die Eigenschaften des Prozessors zu berücksichtigen, um die Suchzeit für eine schnelle Implementierung zu reduzieren.

Im dritten Beitrag befassen wir uns mit der Integration von Anfrageverarbeitungssystemen, die auf der Java Virtual Machine laufen, und solchen, die nativen Maschinencode ausführen. Konkret entwickeln wir zwei Ansätze, um Java-basierte UDF auf einem in C++ geschriebenen Anfrageverarbeitungssystem auszuführen. Im ersten Ansatz wandeln wir eine UDF, die für jedes Tupel ausgeführt wird, in eine UDF um, die einen Block von Tupel verarbeitet, wodurch der Kontextwechsel-Overhead zwischen der Ausführung von C++-Code und der UDF eliminiert wird. Dieser Ansatz funktioniert gut für UDFs, die viele Objekte erzeugen, einschließlich Java-Strings. Im zweiten Ansatz übersetzen wir die Java UDF in Maschinencode und führen sie direkt im C++ Anfragebearbeitungssystem aus. Dieser Ansatz funktioniert gut für rechenintensive UDFs.

Unsere Untersuchung einer Reihe von Szenarien heterogener Hard- und Software zeigt, dass wir bei der Integration dieser Systeme oft vor ähnlichen Herausforderungen stehen. Somit stellen die in dieser Arbeit erarbeiteten Methoden wirksame Bausteine dar, um die Leistungsfähigkeit heutiger heterogener Rechensysteme auszunutzen.

## Contents

| 1. | Intr | oducti | on                                                                    | 1  |

|----|------|--------|-----------------------------------------------------------------------|----|

|    | 1.1. | Hetero | ogeneous hardware and software in the era of big data                 | 1  |

|    |      | 1.1.1. | Drivers of hardware heterogeneity                                     | 2  |

|    |      | 1.1.2. | Drivers of software heterogeneity                                     | 4  |

|    | 1.2. | Thesis | goals and contributions                                               | 6  |

|    |      | 1.2.1. | Query processing on heterogeneous CPU/GPU systems $\ \ldots \ \ldots$ | 7  |

|    |      | 1.2.2. | Operator variant tuning on heterogeneous processors                   | 9  |

|    |      | 1.2.3. | Processing Java UDFs in a C++ environment                             | 11 |

|    | 1.3. | Impac  | t of thesis contributions                                             | 12 |

|    | 1.4. | Struct | ure of the thesis                                                     | 13 |

|    |      |        |                                                                       |    |

| 2. |      |        | cessing on heterogeneous CPU/GPU systems                              | 15 |

|    |      |        | em statement                                                          |    |

|    | 2.2. |        | butions                                                               |    |

|    | 2.3. | Proces | ssor architectures                                                    | 18 |

|    |      | 2.3.1. | Conventional CPUs                                                     | 19 |

|    |      | 2.3.2. | Dedicated GPUs                                                        | 21 |

|    |      | 2.3.3. | GPU integration                                                       | 23 |

|    |      | 2.3.4. | GPU programming model                                                 | 25 |

|    | 2.4. | Evolut | sion of query processing on GPUs                                      | 27 |

|    |      | 2.4.1. | Fixed-function graphics pipelines                                     | 27 |

|    |      | 2.4.2. | Programmable graphics pipelines                                       | 29 |

|    |      | 2.4.3. | General purpose parallel processing                                   | 29 |

|    |      | 2.4.4. | Fast atomic operations                                                | 30 |

|    |      | 2.4.5. | Parallel processing for heterogeneous systems                         | 30 |

|    |      | 2.4.6. | Integrated GPUs                                                       | 31 |

|    |      | 2.4.7. | Inter-kernel communication                                            | 31 |

|    |      | 2.4.8. | Fast coherent interconnects                                           | 32 |

|    |      | 2.4.9. | Hardware accelerated matrix computations                              | 32 |

|    | 3 9  | Contri           | hutions 70                                                          |

|----|------|------------------|---------------------------------------------------------------------|

|    | _    |                  | m statement                                                         |

| 3. | Оре  | rator            | variant tuning on heterogeneous processors 69                       |

|    |      | 2.9.3.           | Conclusion                                                          |

|    |      | 2.9.2.           | Open research problems 6                                            |

|    |      | 2.9.1.           | Performance guidelines                                              |

|    | 2.9. | Key in           | sights and open research problems                                   |

|    |      | 2.8.4.           | Summary                                                             |

|    |      | 2.8.3.           | Discussion                                                          |

|    |      | 2.8.2.           | Classification criteria                                             |

|    |      | 2.8.1.           | Selection criteria                                                  |

|    | 2.8. | System           | n survey                                                            |

|    |      | 2.7.4.           | Summary                                                             |

|    |      | 2.7.3.           | Faster system bus                                                   |

|    |      | 2.7.2.           | Mitigation techniques                                               |

|    |      | 2.7.1.           | Impact of the data transfer bottleneck                              |

|    | 2.7. | _                | ata transfer bottleneck                                             |

|    |      | 2.6.4.           | Summary                                                             |

|    |      | 2.6.3.           | Reverse engineering of GPU hardware details                         |

|    |      | 2.6.2.           | Low-level operator implementations                                  |

|    | 2.0. | 2.6.1.           | High-level query execution plan                                     |

|    | 2.6. |                  | ecture-specific query processing                                    |

|    |      |                  | Summary                                                             |

|    |      | 2.5.9.           | End-to-end integration                                              |

|    |      | 2.5.8.           | Data partitioning                                                   |

|    |      | 2.5.6.<br>2.5.7. | Workload distribution                                               |

|    |      | 2.5.5.           | Scheduling strategy                                                 |

|    |      | 2.5.4.           | Scheduling time                                                     |

|    |      | 2.5.3.           | Processor usage                                                     |

|    |      | 2.5.2.           | Classification overview                                             |

|    |      |                  | Scheduling policy requirements                                      |

|    | 2.5. |                  | aling                                                               |

|    |      |                  | Summary                                                             |

|    |      |                  | Combination of general purpose processing and graphics rendering 3: |

| 3.3. | The o  | perator variant selection problem on heterogeneous hardware $\dots$ 72 |

|------|--------|------------------------------------------------------------------------|

|      | 3.3.1. | Basic selection kernel variants                                        |

|      | 3.3.2. | Low-level implementation parameters                                    |

|      | 3.3.3. | Workload distribution parameters                                       |

|      | 3.3.4. | Variant universe                                                       |

|      | 3.3.5. | Performance analysis on heterogeneous processors                       |

|      | 3.3.6. | Processor diversity                                                    |

|      | 3.3.7. | Influence of workload parameters                                       |

|      | 3.3.8. | Number of competitive variants                                         |

|      | 3.3.9. | Summary                                                                |

| 3.4. | Perfor | mance analysis of hash aggregation on GPUs                             |

|      | 3.4.1. | GPU-accelerated hash aggregation 89                                    |

|      | 3.4.2. | Parallelization strategies                                             |

|      | 3.4.3. | Performance analysis on GPUs                                           |

|      | 3.4.4. | Influence of the parallelization strategy                              |

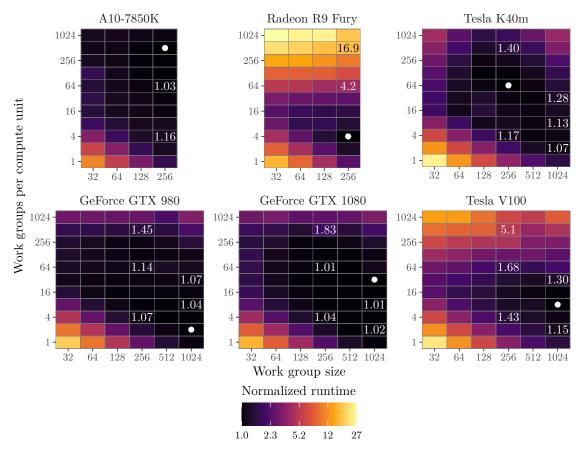

|      | 3.4.5. | Influence of the thread configuration                                  |

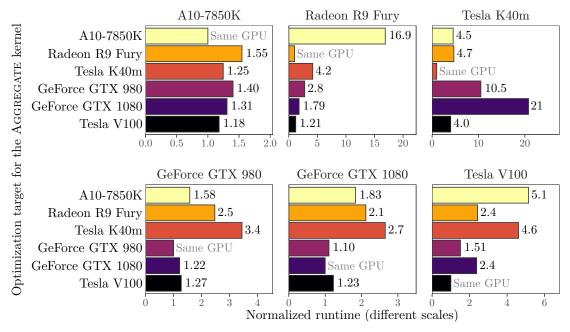

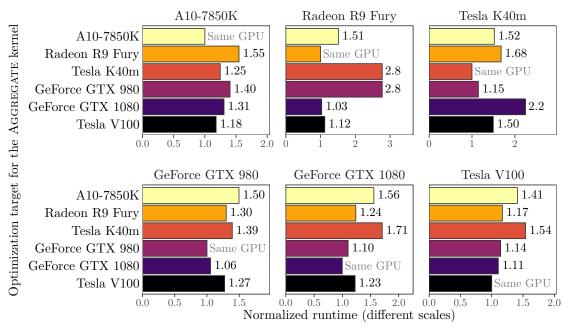

|      | 3.4.6. | Performance penalty of incorrectly optimized Aggregate kernels 97      |

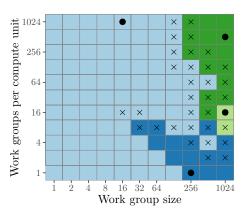

|      | 3.4.7. | Plateaus and minima in the thread configuration search space $100$     |

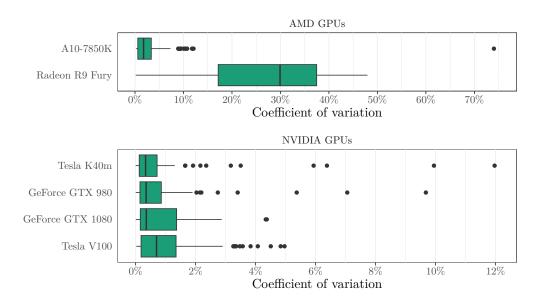

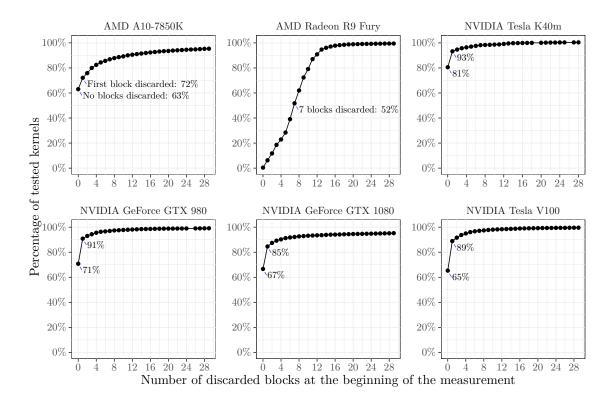

|      | 3.4.8. | Aggregate kernel runtime variation                                     |

|      | 3.4.9. | Summary                                                                |

| 3.5. | Tuning | g operator variants for a specific processor                           |

|      | 3.5.1. | Offline vs. online search                                              |

|      | 3.5.2. | Incorporating information about processor characteristics 106          |

|      | 3.5.3. | Outlook                                                                |

| 3.6. | Candi  | date selection in large variant spaces                                 |

|      | 3.6.1. | Micro adaptivity and the VW-GREEDY algorithm 108                       |

|      | 3.6.2. | Variant pool size limitation                                           |

|      | 3.6.3. | Learning framework overview                                            |

|      | 3.6.4. | Search strategies                                                      |

|      | 3.6.5. | Experimental evaluation                                                |

|      | 3.6.6. | Summary                                                                |

| 3.7. | Runtin | me variation-adaptive local search                                     |

|      | 3.7.1. | Algorithm overview                                                     |

|      | 3.7.2. | Support for other operators                                            |

|      | 3.7.3. | Evaluation                                                             |

|      | 374    | Summary 125                                                            |

|    | 3.8. | Relate  | ed Work                                                          | . 126 |

|----|------|---------|------------------------------------------------------------------|-------|

|    |      | 3.8.1.  | Impact of implementation variants on heterogeneous hardware $$ . | . 126 |

|    |      | 3.8.2.  | Auto-tuning computational kernels                                | . 127 |

|    |      | 3.8.3.  | Database auto-tuning                                             | . 127 |

|    |      | 3.8.4.  | Adaptive query processing                                        | . 128 |

|    | 3.9. | Discus  | ssion and conclusion                                             | . 130 |

|    |      | 3.9.1.  | Processor sensitivity                                            | . 130 |

|    |      | 3.9.2.  | Auto-tuning operator implementations                             | . 131 |

|    |      | 3.9.3.  | Dealing with data and query changes                              | . 132 |

|    |      | 3.9.4.  | Variant and code generation                                      | . 133 |

|    |      | 3.9.5.  | Integration into a query processing system                       | . 134 |

| 4. | Pro  | cessing | g Java UDFs in a C++ Environment                                 | 135   |

|    | 4.1. | Proble  | em statement                                                     | . 135 |

|    | 4.2. | Contri  | ibutions                                                         | . 136 |

|    | 4.3. | Backgr  | round                                                            | . 137 |

|    |      | 4.3.1.  | Scalar UDFs in SparkSQL                                          | . 137 |

|    |      | 4.3.2.  | The Java Native Interface                                        | . 138 |

|    |      | 4.3.3.  | Wildfire                                                         | . 139 |

|    | 4.4. | UDF e   | execution in an embedded JVM                                     | . 141 |

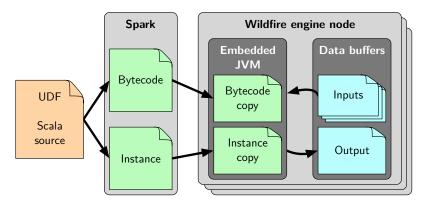

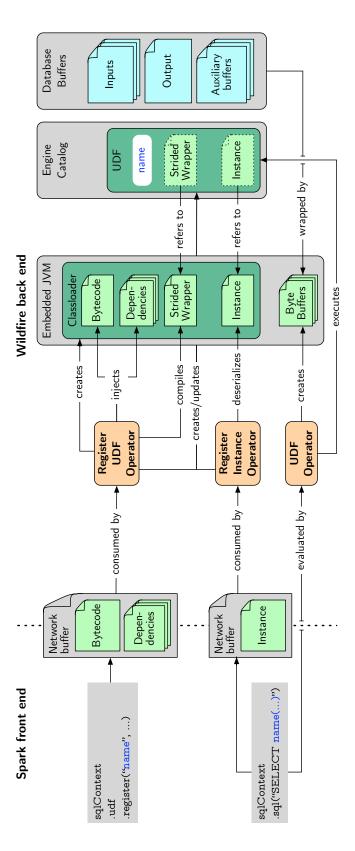

|    |      | 4.4.1.  | Bytecode extraction and transfer                                 | . 141 |

|    |      | 4.4.2.  | Bytecode injection                                               | . 142 |

|    |      | 4.4.3.  | Passing data                                                     | . 143 |

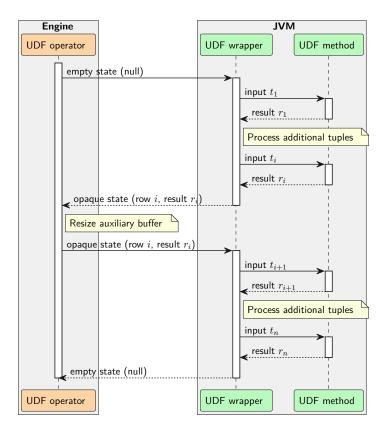

|    |      | 4.4.4.  | Strided execution                                                | . 143 |

|    |      | 4.4.5.  | Detailed architecture                                            | . 145 |

|    |      | 4.4.6.  | User-defined types                                               | . 147 |

|    |      | 4.4.7.  | Security considerations                                          | . 148 |

|    |      | 4.4.8.  | Summary                                                          | . 148 |

|    | 4.5. | Evalua  | ation                                                            | . 149 |

|    |      | 4.5.1.  | Test system and setup                                            | . 149 |

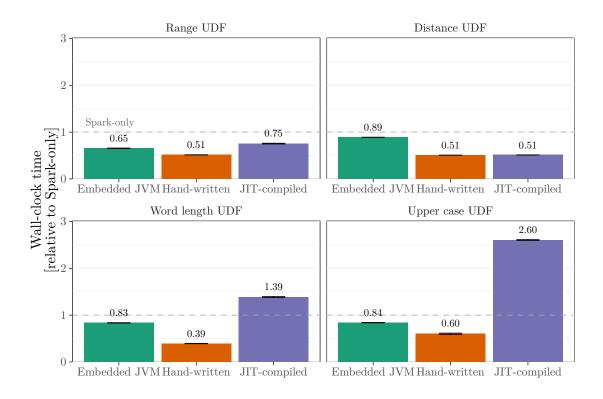

|    |      | 4.5.2.  | Range UDF                                                        | . 150 |

|    |      | 4.5.3.  | Distance UDF                                                     | . 152 |

|    |      | 4.5.4.  | Word length UDF                                                  | . 153 |

|    |      | 4.5.5.  | Upper case UDF                                                   | . 153 |

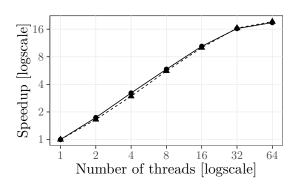

|    |      | 4.5.6.  | Thread scaling                                                   | . 154 |

|    |      | 4.5.7.  | Summary                                                          | . 155 |

|    |      |         |                                                                  |       |

|                        | 4.6.  | Compi   | lation to machine code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 156 |  |

|------------------------|-------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--|

|                        |       | 4.6.1.  | BugVM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 156 |  |

|                        |       | 4.6.2.  | JIT-compiled UDF performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 157 |  |

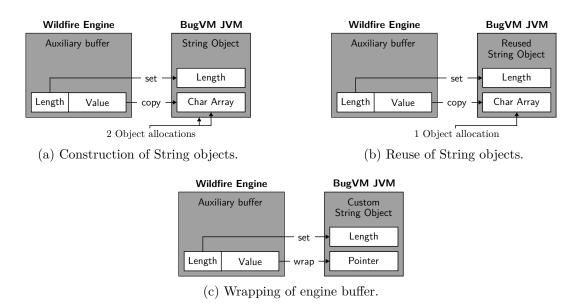

|                        |       | 4.6.3.  | String construction optimizations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 158 |  |

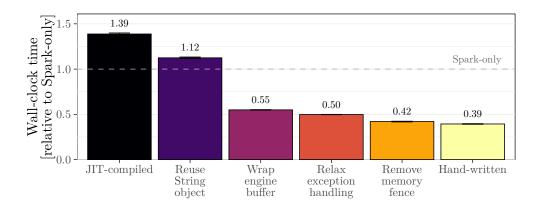

|                        |       | 4.6.4.  | Effect of optimizations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 161 |  |

|                        |       | 4.6.5.  | Applicability of optimizations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 161 |  |

|                        |       | 4.6.6.  | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 162 |  |

|                        | 4.7.  | Relate  | ${ m d}$ work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 162 |  |

|                        |       | 4.7.1.  | Translation to SQL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 163 |  |

|                        |       | 4.7.2.  | Common intermediate representation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 164 |  |

|                        |       | 4.7.3.  | Embedded execution environment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 165 |  |

|                        | 4.8.  | Conclu  | ısion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 166 |  |

| <b>5.</b>              | Con   | clusion | a and research outlook                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 167   |  |

|                        | 5.1.  | Hardw   | rare heterogeneity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 167 |  |

|                        | 5.2.  | Softwa  | re heterogeneity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 170 |  |

|                        | 5.3.  | Comm    | on challenges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 171 |  |

| Α.                     | Des   | criptio | ns of surveyed CPU/GPU query processing systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 173   |  |

| В.                     | Peri  | forman  | ace penalties of incorrectly optimized Aggregate kernels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 183   |  |

| Li                     | st of | Figure  | String construction optimizations       158         Effect of optimizations       161         Applicability of optimizations       161         Summary       162         work       162         Translation to SQL       163         Common intermediate representation       164         Embedded execution environment       165         sion       166         and research outlook       167         re heterogeneity       170         on challenges       171         as of surveyed CPU/GPU query processing systems       173         see penalties of incorrectly optimized AGGREGATE kernels       183         s       187         s       189         s       191 |       |  |

| Li                     | st of | Tables  | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 189   |  |

| Li                     | st of | Listing | ${f gs}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 191   |  |

| List of Algorithms 193 |       |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |  |

| Bi                     | bliog | graphy  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 195   |  |

1

### Introduction

## 1.1. Heterogeneous hardware and software in the era of big data

Big data increasingly shapes decision making in the sciences, industry, and society as a whole [2, 280, 316]. The modern scientific toolbox includes data-driven exploration as an important tool in addition to experimentation, modeling, and simulation [126]. For businesses, data constitute an essential factor of production, similarly to raw materials and human labor [193]. Governments rely on data to increase their operational efficiency and to set public policy [157]. Heterogeneous hardware and software systems underpin these societal trends.

The term big data puts the focus primarily on the amount of data. Indeed, the amount of digital data has grown exponentially since the early 2000s [127]. The world wide web, particularly e-commerce and social media web sites, sensors in mobile devices and the emerging Internet of Things, large scientific experiments, and traditional retail businesses generate datasets that are measured in terabytes and petabytes. However, the era of big data would not be possible without two concurrent trends in computing [2]. First, the exponential growth in computing performance [68], as well as open source software systems, have provided the resources and tools to store and process this abundance of data at greatly reduced costs. And second, data has become democratized. More and more people work with data, not just database administrators and IT specialists, but also business managers, scientists, journalists, and consumers.

When we look at the computing infrastructure to process big data, we find that hardware and software systems are highly heterogeneous [347]. On the hardware side, computing systems contain a large variety of microprocessors with different capabilities, e.g., multi-core processors, graphic processing units (GPUs), digital signal processors (DSPs), tensor processing units (TPUs), or field-programmable gate arrays (FPGAs) [347]. On

the software side, data scientist work with a variety of software environments and programming languages [140]. In part, this heterogeneity is the result of market forces, as hardware manufacturers and software developers continuously refine their products. These market forces in turn are shaped by fundamental trade-offs, which constrain the performance of the computing infrastructure, as products are designed for different market segments. In a nutshell, manufacturers of microprocessors have to trade off microprocessor performance against energy efficiency, whereas software environments trade off application performance against programmer productivity and supported functionality.

This heterogeneity is both a benefit and a challenge. While it enables the tools that allow a diverse set of users to process large data sets, it also increases the complexity of the computing infrastructure. Therefore, in this thesis, we investigate how heterogeneous hardware and software impacts query processing, and develop tools to manage this heterogeneity. Before we describe this thesis' goals and contributions, we motivate the forces that drive hardware and software heterogeneity in more detail.

#### 1.1.1. Drivers of hardware heterogeneity

One of the main constraints on the performance of computing hardware, and specifically of microprocessors, is their power consumption. Since the early 2000s, it has not been economical to increase microprocessor performance by simply increasing their operating speed. To overcome this so-called power wall, the microprocessor industry has pursued three strategies to continue the exponential growth of microprocessor performance. Specifically, modern microprocessors (a) parallelize execution on multiple independent processing cores, and they are either (b) specialized to meet specific application demands, or (c) integrate multiple specialized processing cores.

As a consequence of these three strategies, the processors deployed in today's computing systems are highly heterogeneous. They contain multiple processing cores with diverse characteristics and integrate them in different ways. We can find such heterogeneous systems across the entire range of computing systems, from super computers [321] and cloud infrastructure [15, 92, 202], to consumer laptops [21], mobile devices [255], and embedded industry applications [290]. To achieve high performance, applications running on modern computing system have to take their heterogeneous nature into account and use the available compute resources effectively. They have to match diverse application demands to the most suitable processing core and adapt their algorithms and implementations to the characteristics of the processor that they run on.

The power wall. In the 1980s and 1990s, two mechanisms drove the exponential growth in microprocessor performance. First, processor manufacturers relied on Dennard scaling [67] to reduce the size of transistors and increase their operating frequency. A higher operating frequency means that a microprocessor can execute the same instructions in less time. Second, processors manufacturers exploited the increasing transistor budget to implement large caches as well as microarchitectural advances, such as deep pipelines, branch prediction and speculative execution [125]. These techniques further reduce the latency of individual instructions. Thus, even when programs were left unchanged, their performance increased over time just by running them on a faster processor. Specifically, sequential processor performance doubled every 2.5 years between 1978 and 1986 and every 1.5 years between 1986 and 2003 [124]. Unfortunately, this is no longer the case.

An undesirable side effect of increasing the sequential performance of microprocessors is a corresponding increase in their power consumption, since power consumption scales linearly with operating frequency [125]. By 2003, high-performance commodity CPUs operated at 3 GHz and drew more than 100 Watts [273]. Since then, processor frequencies have stagnated [273]. Increasing them further would produce excessive heat and require cooling solutions that are impractical and uneconomical. Furthermore, the microarchitectural techniques that reduce the latency of individual instructions are not energy-efficient. Over multiple processor generations, their impact on power consumption is quadratic compared to their impact on sequential performance [100].

**Parallelization.** Even though processor frequencies have stagnated, the size of transistors is still shrinking and the number of transistors of modern microprocessors is still increasing [273]. Processor manufacturers utilize this transistor budget to integrate multiple independent processing cores, which run in parallel, in a single microprocessor. Thus, modern processors rely on exploiting data-level parallelism and task-level parallelism to achieve high performance.

**Specialization.** Modern multi-core CPUs integrate a moderate number of parallel processing cores, but these cores are still optimized for sequential performance in order to speed up the inherently sequential parts of an application [39]. Consequently, multi-core CPUs are a good fit for applications which are latency-critical or dominated by sequential execution paths. However, not all applications can be characterized this way.

To meet specific application demands, processor manufacturers have created specialized microprocessor designs. For example, GPUs are optimized for throughput performance to speed up applications that are highly data-parallel [182]; TPUs are optimized

for low-precision matrix operations which are commonly found in deep learning applications [138]; FPGAs allow developers to create processors that are customized to a specific application [79]; digital signal processors (DSPs) process (digitized) analog signals, such as sounds, speech, images, videos, or radar pulses [73]; neuromorphic processors [66, 197] emulate the behaviors and properties biological neurons; and molecular dynamics processors [232, 285] simulate biological molecules at the atomic level. Specialized processors avoid allocating transistors on hardware features that do not fit application demands, which enables them to achieve higher performance than general-purpose processors while staying in the same power budget.

Integration. GPUs, TPUs, and FPGAs are originally designed as dedicated coprocessors, which are connected to a traditional multi-core CPU over a system bus. Alternatively, multiple specialized processing cores can also be integrated into a single asymmetric and/or heterogeneous multi-core processor. Asymmetric multi-core processors (AMPs) combine a small number of complex high-performance cores with a large number of simple low-performance cores to speed up both the latency-critical sequential parts as well as the throughput-critical parallel parts of an application [128]. Compared to traditional multi-core processors, in which all cores are of the same design, AMPs can achieve better overall performance within the same transistor budget [128].

Heterogeneous multi-core processors, which integrate specialized processing cores to support specific applications in a highly power-efficient way, achieve even better performance than AMPs for parallel workloads [57]. Such processors can reduce the operating frequency of different processing cores to balance the power budget according to application demands [41], or turn off individual cores completely when they are not in use [168]. Moving data between specialized cores is also faster and requires less energy than moving it between the CPU and a dedicated coprocessor, because the cores are physically closer together and are connected by an on-chip interconnect [21].

#### 1.1.2. Drivers of software heterogeneity

We can identify at least three factors that lead to heterogeneous software systems. First, specialized computing hardware, such as the specialized microprocessors we discussed in the previous section, has to be programmed with dedicated programming tools. Second, programmers themselves are not a homogeneous group and require different software environments to be productive, depending on their skill set and the priorities imposed by the problem they want to solve. And third, the complexity and variety of data analysis and other programming tasks often require specialized tools at different stages.

As a consequence, we have to integrate separate software components into a heterogeneous software ecosystem, in order to enable different users perform complex data analysis tasks in a way that meets their skills and their performance requirements. Consider, for example, the ecosystem created around Apache Hadoop [309]. Since its initial release, a large number of software systems have been released, which either build upon Hadoop, or provided specialized services, e.g., Apache Hive [310], a distributed data warehouse; Apache Mahout [311], a distributed machine learning library; and Zookeeper [314], a coordination service for distributed applications. Later data analytics systems, e.g., Apache Spark [345] and Apache Flink [51], improve on Hadoop's capabilities, but maintain a high degree of compatibility. For example, they can interoperate with services such as the Hadoop Distributed File System (HDFS) [287], use common data formats such as Apache Avro [307] and Apache Parquet [312], and are even able to reuse user-defined functions (UDFs) written for Hadoop [59].

Heterogeneous hardware. The specialization of computing hardware directly leads to heterogeneous software environments. For each processor type, there are low-level programming languages or language constructs, which provide the necessary programming abstractions to match the processor design, and offer a high degree of control over the hardware. For example, on multi-core CPUs, pthreads [210] and OpenMP [65] are C language constructs to implement task parallelism and data parallelism, respectively; NVIDIA provides CUDA [211] as a dedicated programming environment for NVIDIA GPUs; similarly, Google provides TensorFlow [5] to program TPUs; and circuits for FPGAs are often implemented in the low-level hardware description languages Verilog [320] and VHDL [22]. Consequently, programmers have to employ multiple programming frameworks to develop applications which utilize specialized processors in heterogeneous computing systems.

Diverse user requirements. Programmers are a very diverse group with different skill sets, different motivations to write software, and different performance needs. We can distinguish between novice and expert programmers; amateurs and professionals; as well as regular programmers, for whom software development is the main professional activity, and casual programmers, such as data scientists or researchers, who write programs as a means to some other professional end [158]. These groups require different programming environments to work productively and will trade off application performance to a different degree. Expert programmers prefer programming languages that let them concisely express an abstract solution using high-level constructs, but also provide low-level control over the hardware, which is the key to predictable performance [246].

In contrast, casual programmers often choose high-level programming languages with rich libraries that allow them to quickly develop solutions to their problems [131]. For example, Python [254] is a popular programming language among data scientists because it includes powerful libraries for statistical analysis, machine learning, and data mining applications [140, 251]. These libraries provide so much value that data scientists choose Python even though it is about  $50 \times$  slower than an equivalent, unoptimized C program, and  $60000 \times$  slower than an optimized version [124].

High-level languages, such as Python, target traditional CPUs and do not support specialized processors out of the box. Libraries in these languages have to achieve two objectives. On the one hand, they have to provide the domain-specific functionality required by casual programmers, such as data scientists. On the other hand, they have to transparently support multiple processing cores and specialized processors, so that data scientists can benefit from improved application performance. Consequently, modern heterogeneous software environments bridge high-level and low-level programming languages, in order to resolve the tension between programmer productivity and application performance.

Complexity of data analysis tasks. The complexity and variety of today's data analysis tasks are additional factors which results in heterogeneous software environments. Commonly expressed by the phrase "one size does not fit all", the demands of a particular application scenario, such as analytical processing or stream processing, prompt a specific software implementation to include functionality that is of no use to other applications, or even degrades their performance [301]. Moreover, a data processing task may benefit from, or even require, the combination of multiple software systems in a complex data processing pipeline [10, 143]. For example, if the data is stored in multiple locations and/or formats, or if the system in which the data is stored does not support a specific analysis method, a complex data processing pipeline has to involve multiple systems in order to complete the task. In other cases, splitting a complex task into smaller steps and executing each step on a specialized system improves overall performance.

#### 1.2. Thesis goals and contributions

As we have seen, heterogeneous hardware and software are an integral part of today's computing systems. This heterogeneity is both a challenge and an opportunity for query processing. On the one hand, system developers have to adapt query processing code to exploit the computing power of specialized processors, in order to deal with the

increasing processing demands of big data. On the other hand, integrating multiple software systems to improve user productivity while retaining high performance, is the key to solve complex data processing tasks and provide access to many users, in order to further democratize data analysis. Therefore, this thesis has the following two goals.

Thesis goals -

- (1) Investigate how heterogeneous hardware and software impacts query processing.

- (2) Develop techniques to achieve high query processing performance on heterogeneous hardware and software systems.

Since hardware and software heterogeneity is a very broad topic, we focus on three specific scenarios to reduce the scope of this thesis. In the following, we discuss the heterogeneous aspect of each scenario, develop the specific research goals and questions, and summarize our results and contributions.

#### 1.2.1. Query processing on heterogeneous CPU/GPU systems

In the first scenario, we investigate the impact of heterogeneous processing architectures on query processing.

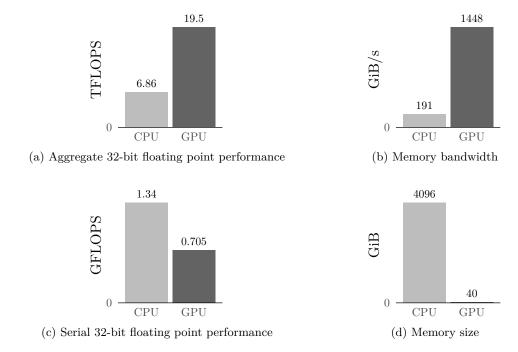

Heterogeneous aspect. A heterogeneous CPU/GPU system is a computing system which contains both CPUs and GPUs as processors. We call a query processing system which exploits both CPUs and GPUs for query processing a heterogeneous query processing system. A heterogeneous query processing system has to address three challenges in order to effectively exploit the processing power of heterogeneous CPU/GPU systems.

- (1) CPUs and GPUs are optimized for different applications and therefore have different capabilities. It follows that some tasks of a query processing system may run faster on the CPU and other tasks may run faster on the GPU. A heterogeneous query processing system has to distribute the query processing workload on processors with different capabilities in a way that exploits the strengths of each processor and avoids their weaknesses.

- (2) CPUs and GPUs have to be programmed differently. A major difference between both processors is how they employ multiple threads to solve a complex problem. On CPUs, threads typically work on independent subproblems, whereas on GPUs, groups of threads have to cooperate to achieve high performance. A heterogeneous query pro-

cessing system has to support implementations for multiple processors efficiently, i.e., without increasing development and maintenance costs.

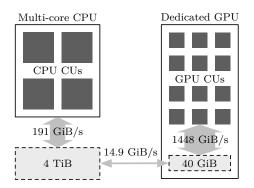

(3) CPUs and GPUs can be integrated in different ways which affects the speed at which the GPU can access data in memory. Dedicated GPUs must transfer data from system main memory over a slow interconnect before they can process it. A heterogeneous query processing system has to overcome this data transfer bottleneck.

**Research goals.** In this part of the thesis, we study how heterogeneous query processing systems address these three challenges. Specifically, we focus on the following research goals.

- Research goals (first scenario) ———

- (1.1) Review and classify techniques to distribute a query processing workload on CPUs and GPUs, to program heterogeneous CPU/GPU systems efficiently, and to overcome the data transfer bottleneck.

- (1.2) Classify heterogeneous query processing systems according to the techniques which they employ, and identify best practices and open research problems.

**Contributions.** In this part of the thesis, we make the following contributions.

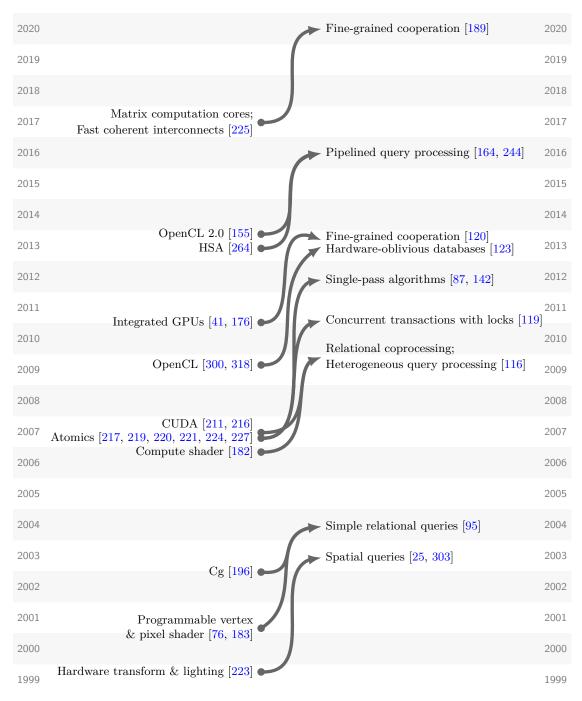

- (1) For our review, we conduct a survey of the academic literature on query processing on heterogeneous CPU/GPU systems. Our survey covers a diverse set of complete query processing systems, e.g., relational query processors, stream processing systems, hybrid analytical/transactional systems, and key value stores; as well as implementations which perform a specific query processing tasks, including joins, sorting, indexing, and spatiotemporal query processing.

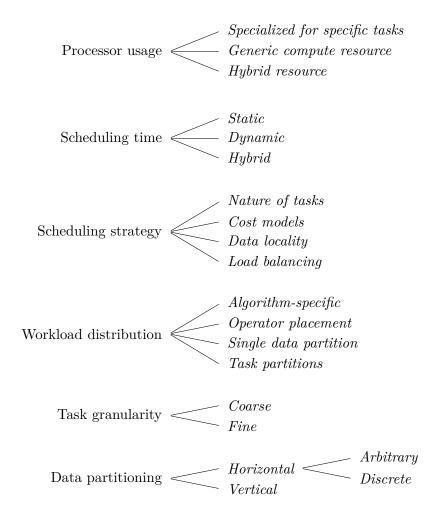

- (2) We develop a classification scheme to categorize techniques to distribute a query processing workload on CPUs and GPUs.

- (3) Based on this classification scheme, and a review of the techniques to program heterogeneous CPU/GPU systems efficiently and to overcome the data transfer bottleneck, we categorize the surveyed query processing systems. This classification allows us to identify common strategies to overcome performance bottlenecks, as well as to identify query processing tasks which have not yet been investigated on heterogeneous CPU/GPU systems.

- (4) We summarize the history of employing GPU hardware for query processing and identify GPU hardware which has not yet been broadly studied in the context of query processing.

**Key insights.** The key insight of our review is that heterogeneous CPU/GPU systems with dedicated and integrated GPUs require different strategies to distribute the workload on CPU and GPU in order to achieve high performance.

The major limiting factor of query processing performance of heterogeneous CPU/GPU systems with dedicated GPUs is the data transfer bottleneck between the CPU and the GPU. To mitigate the effect of this bottleneck, query processing systems targeting dedicated GPUs should offload specialized coarse-grained tasks to the GPU. This strategy largely precludes fine-grained cooperation between the CPU and the GPU because such cooperation relies on the frequent and low-latency exchange of data.

In contrast, heterogeneous CPU/GPU system with integrated GPUs are not constrained by the data transfer bottleneck. Instead, the CPU and the GPU in such systems are connected by a fast and cache-coherent on-chip fabric which enables both processors to modify shared data structures simultaneously. Query processing systems targeting integrated GPUs can divide the workload into fine-grained cooperative tasks and assign each task to a processor that best matches its processing characteristics.

Basis of work. The content described in this part of the thesis was published in ACM Computing Surveys Volume 55, Issue 1, in 2022 [266].

#### 1.2.2. Operator variant tuning on heterogeneous processors

In the previous scenario, we examined the challenges of query processing on multiple heterogeneous processor architectures in a comprehensive fashion. In the second scenario, we drill down on a specific aspect of such a query processing system: its low-level operator implementation.

Heterogeneous aspect. To achieve high performance, the operator implementation of a query processing system has to be tailored to the specific processor it runs on. The developers of a query processing system have many degrees of freedom when designing its operator implementation. For example, they have to decide how to parallelize the workload and distribute it on multiple threads, which data structures to use, and whether to apply low-level optimizations, such as branch-free execution.

One approach to develop a heterogeneous query processing system is to include hand-written operator implementations for each targeted processor architecture. For example, GDB [116] contains two completely separate operator implementations, one written in CUDA [211] for NVIDIA GPUs, and one written in OpenMP [65] for multi-core CPUs. This approach incurs substantial development and maintenance costs as the number of targeted processor architectures, and programming frameworks we need to use, increases.

The developers have to manually tune a specialized operator implementation for each target architecture, and then they have to maintain this implementation as the query processing system evolves.

**Research goals.** In this part of the thesis, we aim to mitigate the costs of supporting multiple operator implementations in a heterogeneous query processing system, by letting the system automatically adapt its operator implementation to the processor it runs on. Specifically, we focus on the following research questions.

- Research questions (second scenario) -

- (2.1) How sensitive are processors to changes in the operator implementations?

- (2.2) How can a query processing systems learn fast operator implementations automatically, without manual tuning?

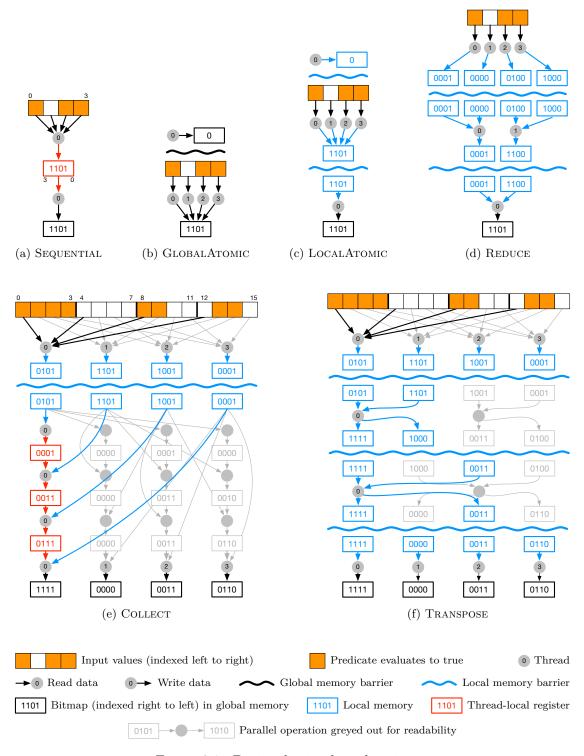

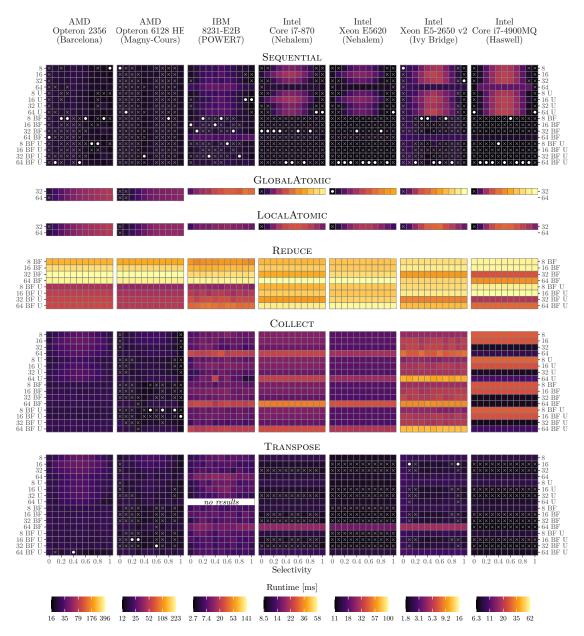

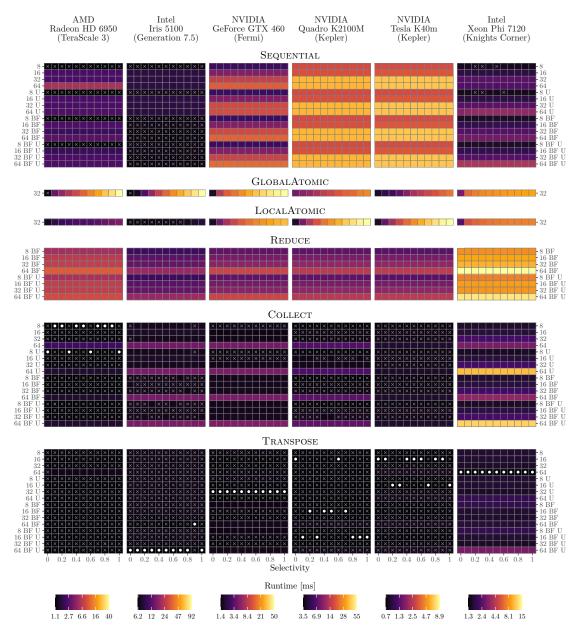

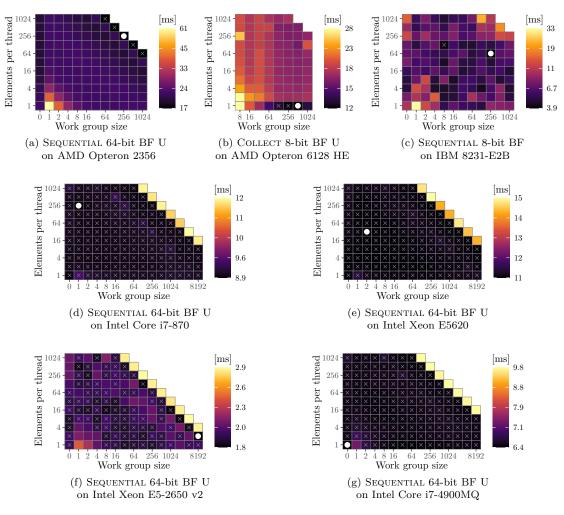

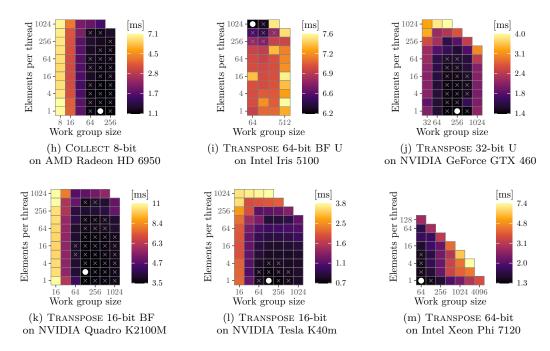

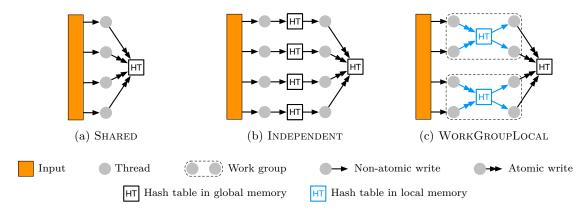

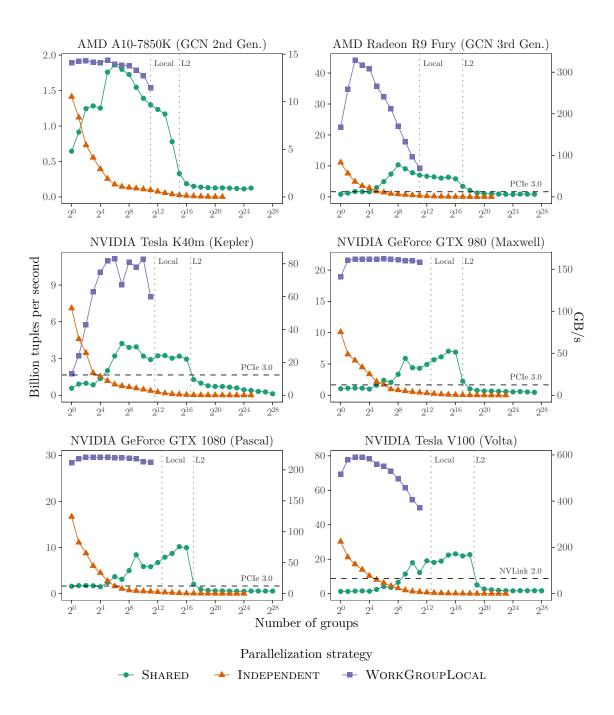

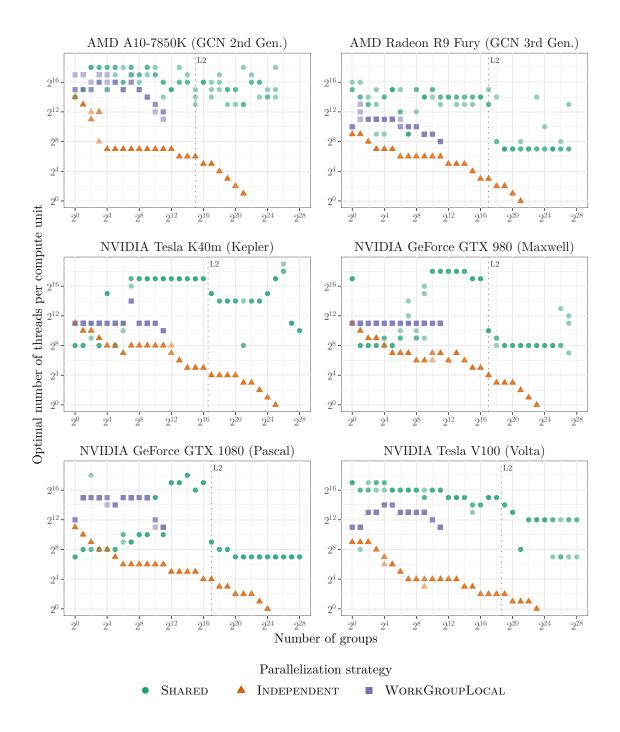

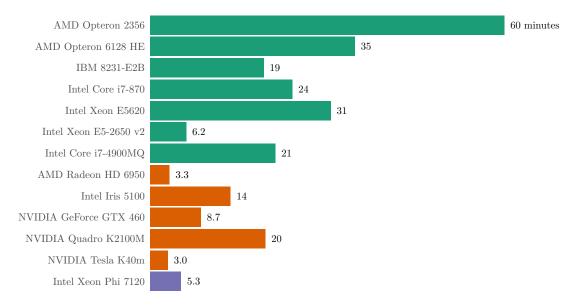

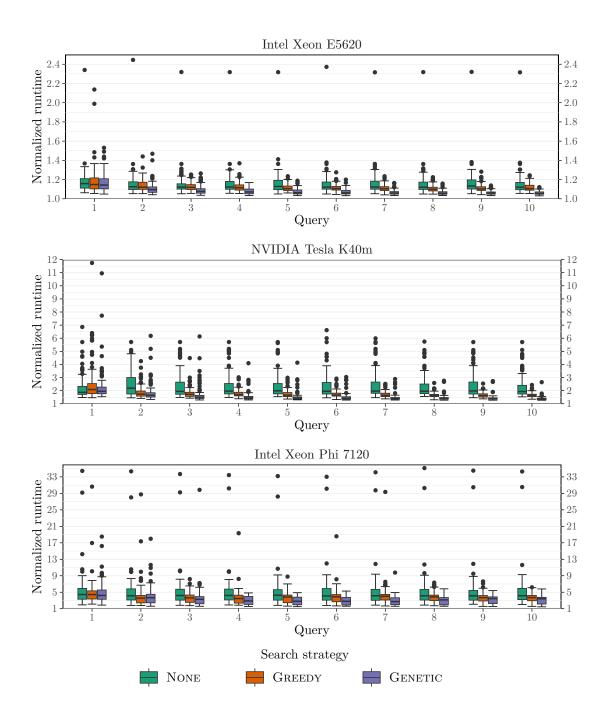

Contributions and results. Our first two contributions are an extensive experimental performance analysis of two common database operators, i.e., selection and hash aggregation, on multiple processor architectures, including multi-core CPUs, GPUs, and a Xeon Phi coprocessor. Even with these simple operations, a small number of implementation parameters yield a large search space, consisting of hundreds, or even thousands, of possible operator implementations. We find that the best operator implementation depends on the specific processor. Implementation heuristics derived from analyzing one processor are not necessarily transferable to other processors, even if they are based on similar microarchitectures by the same vendor. Furthermore, our analysis reveals that some processors are more difficult to optimize for, because any deviation from a specific set of implementation parameters incurs a significant performance penalty. In contrast, on other processors, many different implementations are competitively fast.

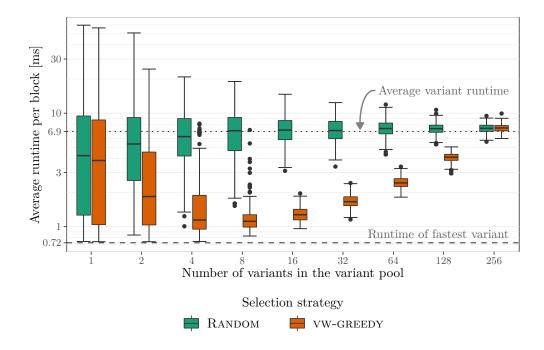

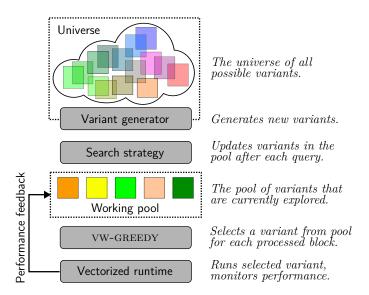

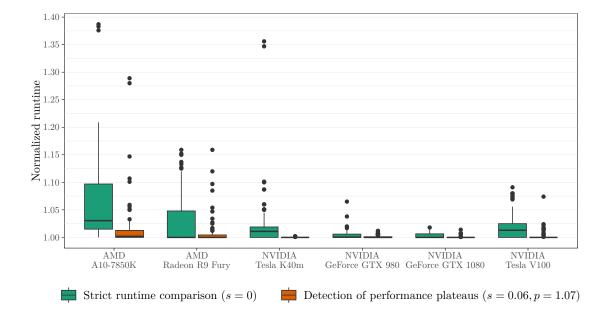

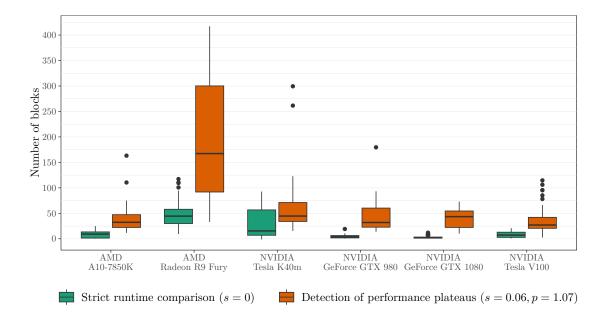

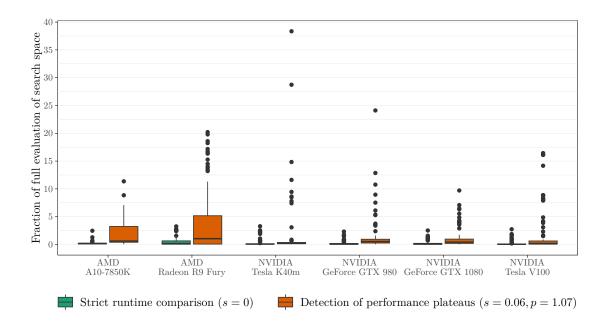

Our third and fourth contributions are two algorithms which enable a query processing system find fast operator implementations at runtime during query execution. The first algorithm extends micro adaptivity [258] with a search strategy to handle a large number of possible operator implementation candidates. The second algorithm extends a local search to handle performance plateaus and variations in operator runtime to overcome local optima in the search space. The key insight of our analysis of these two algorithms is that it is necessary to exploit information about the processor and the search space to reduce the search time for a fast variant.

Basis of work. The content described in this part of the thesis is based on two publications presented at ADMS 2015 [268] and at DaMoN 2019 [267].

#### 1.2.3. Processing Java UDFs in a C++ environment

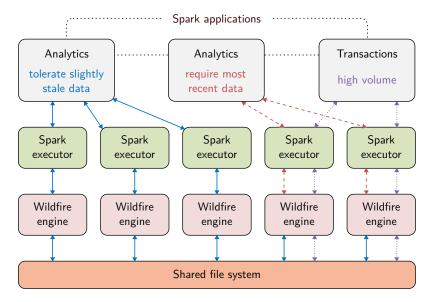

Whereas the previous two scenarios focused on the effect of hardware heterogeneity on query processing, in this scenario, we focus on software heterogeneity. Specifically, this scenario is motivated by an effort to extend Apache Spark [345] with the ability to process transactions, while retaining the familiar SparkSQL [20] user interface for analytical queries. To this end, we replace the exiting Spark execution engine with Wildfire [26], a hybrid transactional/analytical engine.

Heterogeneous aspect. Whereas Apache Spark is written in Scala [74], a programming language that is compiled to bytecode which runs on the Java Virtual Machine (JVM) [184], the Wildfire engine is written in C++, which is compiled to machine code that executes natively on the processor. This difference in programming language presents a challenge when executing SparkSQL queries with user-defined functions (UDFs) in Wildfire: How can we execute arbitrary code that is written in a JVM-based language inside a query engine that does not run on the JVM.

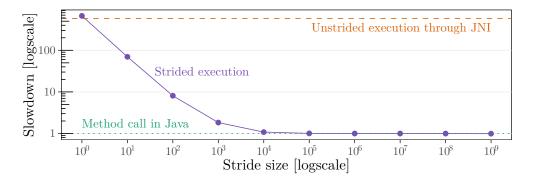

The JVM specification provides a standardized mechanism, the Java Native Interface (JNI) [234], to integrate with programs which are written in other programming languages. Through the JNI, a program can instantiate an embedded JVM and execute Java bytecode inside it. However, a JNI call is orders of magnitude slower than a simple function call in Java or in a compiled language such as C++. This overhead is significant if we have to use the JNI to invoke a Java-based UDF from C++ for every data tuple processed by a SparkSQL query.

**Research goals.** In this part of the thesis, we aim to improve the interoperability of UDF-based query processing systems which run on the JVM and those implemented in other programming languages. Specifically, we focus on the following research questions.

- Research questions (third scenario) —

- (3.1) How can we mitigate the overhead of calling Java UDFs over JNI from C++ code for every data tuple?

- (3.2) Can we bypass the JNI entirely and call Java UDFs directly from C++ code?

- (3.3) How can a query processing system, which is written in a language that compiles to machine code such as C++, execute tuple-based Java UDFs efficiently and transparently to the user?

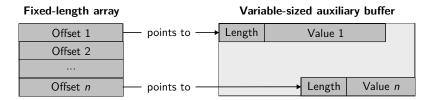

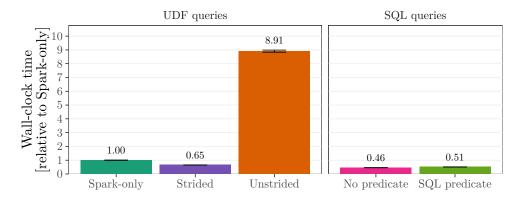

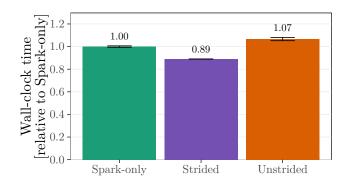

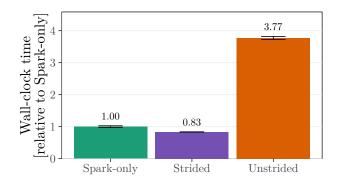

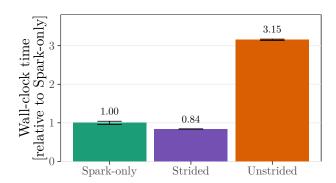

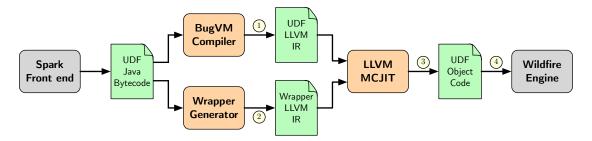

Contributions and results. We develop two approaches to reduce the overhead of calling tuple-based Java UDFs from C++. In the first approach, we transparently generate a strided execution wrapper to transform a UDF which processes a single tuple into a UDF which processes a batch of tuples. By amortizing the cost of a single JNI call over multiple input tuples, this approach matches the performance of executing the Java UDF inside the original JVM-based query processing system. In the second approach, we compile the bytecode of the Java UDF into machine code and link it directly with a C++ query processing engine. This approach bypasses the JNI entirely.

Comparing these two approaches shows that compiling a Java UDF into machine code is faster if the UDF is compute-intensive and does not create many Java objects. However, if the UDF does create many objects, including Java strings, it is faster to transform a tuple-based UDF into a batch UDF and execute it inside an embedded JVM.

Basis of work. The content described in this part of the thesis was published at ACM SoCC 2017 [269].

#### 1.3. Impact of thesis contributions

**Publications of thesis contributions.** The primary results of this thesis are based on four publications, which have been presented at international conferences and workshops, or published in a journal.

- V. Rosenfeld, M. Heimel, C. Viebig, and V. Markl. 2015. The operator variant selection problem on heterogeneous hardware. In *Proc. of ADMS@VLDB'15*, 1–12

- V. Rosenfeld, R. Mueller, P. Tözün, and F. Özcan. 2017. Processing Java UDFs in a C++ environment. In *Proc. of ACM SoCC'17*, 419–431. DOI: 10.1145/3127 479.3132022

- V. Rosenfeld, S. Breß, S. Zeuch, T. Rabl, and V. Markl. 2019. Performance analysis and automatic tuning of hash aggregation on GPUs. In *Proc. of DaMoN'19*. DOI: 10.1145/3329785.3329922

- V. Rosenfeld, S. Breß, and V. Markl. 2022. Query processing on heterogeneous CPU/GPU systems. *ACM Comput. Surv.*, 55, 1. DOI: 10.1145/3485126

Open source contributions. We have released the source code and experiments which make up our second research scenario, i.e., operator variant tuning on heterogeneous processors, under the Apache License 2.0.

- https://git.tu-berlin.de/viktor-rosenfeld/perseus. This repository contains our OpenCL implementations of the selection operator, as well a C++ implementation of the variant tuning framework to learn fast operators at runtime.

- https://git.tu-berlin.de/viktor-rosenfeld/gpu-hash-aggregation-analysis. This repository contains our OpenCL implementations of the hash aggregation operator, as well as a Python implementation of our local search algorithm to handle performance plateaus and runtime variation.

**Additional publications.** In addition, the author collaborated on the following two publications while working on this thesis.

- T. Behrens, V. Rosenfeld, J. Traub, S. Breß, and V. Markl. 2018. Efficient SIMD vectorization for hashing in OpenCL. in *Proc. of EDBT'18*, 489–492. DOI: 10.544/002/edbt.2018.54

- C. Kotselidis, I. Komnios, O. Akrivopoulos, S. Bress, K. Doka, H. Mohammed, G. Mylonas, V. Spitadakis, D. Strimpel, J. Fumero, F. S. Zakkak, M. Papadimitriou, M. Xekalaki, N. Foutris, A. Stratikopoulos, N. Koziris, I. Konstantinou, I. Mytilinis, C. Bitsakos, C. Tsalidis, C. Tselios, N. Kanakis, C. Lutz, V. Rosenfeld, and V. Markl. 2020. Efficient compilation and execution of JVM-based data processing frameworks on heterogeneous co-processors. In *Proc. of DATE'20*, 175–179. DOI: 10.23919/DATE48585.2020.9116246

#### 1.4. Structure of the thesis

The remainder of this thesis is structured as follows.

Chapter 2. In this chapter, we focus on query processing on heterogeneous hard-ware, specifically on systems that contain both CPUs and GPUs. We identify three key challenges that such heterogeneous systems present, i.e., that a query processing system has to distribute the workload on processors with different capabilities; that the implementation of the query processing system has to be adapted to both processors; and that the query processing system has to mitigate the slow connection between the CPU and GPU. We then conduct a survey of the academic literature to review, describe, and

classify techniques which address these challenges. Based on our survey, we formulate performance guidelines for query processing on heterogeneous CPU/GPU systems.

Chapter 3. Next, we focus on a specific challenge of query processing on heterogeneous hardware, i.e., the need to adapt the query processing code to different processors. We show that even a few implementation parameters create a large optimization space containing thousands of different implementation variants and that GPUs are especially sensitive to the selection of optimal implementation parameters. To reduce the cost of manual tuning and maintaining multiple specific implementations in a code base, we develop two algorithms to find fast implementations at runtime.

Chapter 4. In this chapter, we focus on query processing in a heterogeneous software environment, specifically the integration of query processing systems written in a JVM-based language and systems written in a compiled language. We develop two approaches, strided execution inside an embedded JVM and JIT-compilation of the Java bytecode, to execute Java-based UDFs containing arbitrary code inside a query engine written in C++. Our approaches mitigate or eliminate the large runtime overheads typically associated with calling Java code from C++ for each processed tuple.

**Chapter 5.** We conclude this thesis by discussing open research questions for future work.

**Appendices.** Additionally, in Appendix A, we discuss the scheduling decisions of selected heterogeneous query processing systems, which we surveyed in Chapter 2. In Appendix B, we provide comprehensive data from experiments performed in Chapter 3.

## Query processing on heterogeneous CPU/GPU systems

#### 2.1. Problem statement

To process the vast amount of data generated by businesses and scientific communities, data processing engines need to take advantage of heterogeneous processor architectures integrated in modern computing systems [3]. Indeed, the research community has embraced data processing on heterogeneous processors such as graphics processing units (GPUs) [45, 116, 286], field-programmable gate arrays (FPGAs) [79, 134, 305], and asymmetric multi-core processors (AMPs) [204].

In this chapter, we conduct a comprehensive review of the impact of heterogeneous CPU/GPU systems on query processing, i.e., computing systems which contain both multi-core CPUs and GPUs as processors. We focus on GPUs because they have been one of the most successful specialized processors in the last two decades. Not only are GPUs ubiquitous in consumer electronics, e.g., mobile phones and laptops [21, 255], but they are also commonly used in cloud environments [15, 92, 202], super computer installations [321], and embedded industry applications [290]. Compared to AMPs, which are geared towards the mobile market, GPUs provide significant processing power. Compared to FPGAs, they are much simpler to program [79].

Just as hardware is becoming increasingly diverse, so are the applications that process data and the demands these applications place on query processing systems. Traditional database systems process queries that are based on relational algebra [23]. Relational queries consist of *selections* and *projections* to filter and transform data; *joins* to combine multiple data sources; *groupings* and *aggregations* to categorize and summarize

data; as well as set operations. Online analytical processing (OLAP) systems perform interactive, analytical queries over large, multi-dimensional data sets to support business decisions [135]. OLAP queries are dominated by joins and grouped aggregations. Hybrid transactional/analytical (HTAP) systems integrate transactional and analytical workloads in one system to support analytical queries over up-to-date data. Spatial query systems operate on data that represents geometrical primitives, i.e., points, lines, and polygons, as well as non-spatial, relational data [75]. Whereas the previously described systems operate on stored data, stream processing systems [1, 51] operate on continuously updating streams of data and order them according to a time domain [63]. Stream queries process data in terms of windows, which define the portions of the input that are considered during query execution.